# ERIKA Enterprise Manual for the Altera Nios II target

the multicore RTOS on FPGAs

version: 1.2.1 March 5, 2009

### About Evidence S.r.l.

Evidence is a spin-off company of the ReTiS Lab of the Scuola Superiore S. Anna, Pisa, Italy. We are experts in the domain of embedded and real-time systems with a deep knowledge of the design and specification of embedded SW. We keep providing significant advances in the state of the art of real-time analysis and multiprocessor scheduling. Our methodologies and tools aim at bringing innovative solutions for next-generation embedded systems architectures and designs, such as multiprocessor-on-a-chip, reconfigurable hardware, dynamic scheduling and much more!

### **Contact Info**

Address: Evidence Srl, Via Carducci 64/A Località Ghezzano 56010 S.Giuliano Terme Pisa - Italy Tel: +39 050 991 1122, +39 050 991 1224 Fax: +39 050 991 0812, +39 050 991 0855

For more information on Evidence Products, please send an e-mail to the following address: info@evidence.eu.com. Other informations about the Evidence product line can be found at the Evidence web site at: http://www.evidence.eu.com.

This document is Copyright 2005-2008 Evidence S.r.l.

Information and images contained within this document are copyright and the property of Evidence S.r.l. All trademarks are hereby acknowledged to be the properties of their respective owners. The information, text and graphics contained in this document are provided for information purposes only by Evidence S.r.l. Evidence S.r.l. does not warrant the accuracy, or completeness of the information, text, and other items contained in this document. Matlab, Simulink, Mathworks are registered trademarks of Matworks Inc. Microsoft, Windows are registered trademarks of Microsoft Inc. Java is a registered trademark of Sun Microsystems. OSEK is a registered trademark of Siemens AG. The Microchip Name and Logo, and Microchip In Control are registered trademarks or trademarks of Microchip Technology Inc. in the USA. and other countries, and are used under license. All other trademarks used are properties of their respective owners. This document has been written using LaTeX and LyX.

# Contents

| 1 | Intro | Introduction 5                                                            |                |  |  |  |  |  |  |

|---|-------|---------------------------------------------------------------------------|----------------|--|--|--|--|--|--|

|   | 1.1   | Erika Enterprise on multicores                                            | 5              |  |  |  |  |  |  |

|   |       | 1.1.1 Systems-On-Chip and FPGAs: the future?                              | 5              |  |  |  |  |  |  |

|   | 1.2   | Solving problems when moving code to multicores                           | 6              |  |  |  |  |  |  |

|   |       | 1.2.1 Design and programming.                                             | 7              |  |  |  |  |  |  |

|   |       | 1.2.2 Code placement and resource sharing                                 | 7              |  |  |  |  |  |  |

|   |       | 1.2.3 Porting of legacy code to new architectures and to multicores       | $\overline{7}$ |  |  |  |  |  |  |

|   |       | 1.2.4 Resource sharing and OS-level mechanisms.                           | 8              |  |  |  |  |  |  |

|   | 1.3   | Multicore API implementation                                              | 8              |  |  |  |  |  |  |

|   |       | 1.3.1 Erika Enterprise and multicore hiding                               | 8              |  |  |  |  |  |  |

|   |       | 1.3.2 Contention for multicore shared data structures                     | 9              |  |  |  |  |  |  |

|   | 1.4   | Erika Enterprise for the Altera NIOS II platform                          | 10             |  |  |  |  |  |  |

| 2 | Sing  | le CPU designs                                                            | 14             |  |  |  |  |  |  |

|   | 2.1   | Single core Design Flow                                                   | 14             |  |  |  |  |  |  |

|   | 2.2   | System libraries                                                          | 14             |  |  |  |  |  |  |

|   | 2.3   | Interrupts                                                                | 16             |  |  |  |  |  |  |

|   | 2.4   | The StartOS function                                                      | 16             |  |  |  |  |  |  |

|   | 2.5   | Altera Nios II IDE tips and tricks                                        | 17             |  |  |  |  |  |  |

|   | 2.6   | Altera Device Drivers                                                     | 18             |  |  |  |  |  |  |

| 3 | Mul   | ticore designs                                                            | 19             |  |  |  |  |  |  |

|   | 3.1   | Multicore Design Flow                                                     | 19             |  |  |  |  |  |  |

|   | 3.2   | Basic notions                                                             | 20             |  |  |  |  |  |  |

|   | 3.3   | Data scopes                                                               | 22             |  |  |  |  |  |  |

|   | 3.4   | Memory types and their allocation                                         | 25             |  |  |  |  |  |  |

|   | 3.5   | Handling data consistency using mutual exclusion                          | 28             |  |  |  |  |  |  |

|   | 3.6   |                                                                           |                |  |  |  |  |  |  |

|   | 3.7   | Interprocessor Interrupt                                                  | 32             |  |  |  |  |  |  |

|   | 3.8   | Data caches and multicore data sharing                                    | 34             |  |  |  |  |  |  |

|   |       | 3.8.1 How to define cache-disabled multicore global data structures       | 37             |  |  |  |  |  |  |

|   |       | 3.8.2 How to define a data structure that is global to a single processor | 39             |  |  |  |  |  |  |

|   |       | 3.8.3 How to allocate a data structure inside a particular data memory    | 40             |  |  |  |  |  |  |

|   |       | 3.8.4 Disabling GP addressing for global resource access                  | 40             |  |  |  |  |  |  |

|   | 3.9   | Code sharing                                                              | 41             |  |  |  |  |  |  |

|   |       | On-chip memories, .hex files and multicore systems                        | 42             |  |  |  |  |  |  |

|   | 3.11  |                                                                           | 43             |  |  |  |  |  |  |

| Contents |  |

|----------|--|

|----------|--|

| 4 | OIL  | Extens  | ions for the Nios II target          | 45 |

|---|------|---------|--------------------------------------|----|

|   | 4.1  | Task E  | Ixtensions                           | 45 |

|   |      | 4.1.1   | Stack size                           | 45 |

|   | 4.2  | Nios II | specific extensions                  | 45 |

|   |      | 4.2.1   | Configuration parameters             | 45 |

|   |      | 4.2.2   | CPU data                             | 46 |

|   |      | 4.2.3   | Mutex options                        | 47 |

|   |      | 4.2.4   | Startup                              | 47 |

|   |      | 4.2.5   | Intertask notifications              | 48 |

|   |      | 4.2.6   | Compiler options                     | 48 |

|   | 4.3  | OIL E   | xtensions for Multiprocessing        | 49 |

|   |      |         | Interprocessor Interrupts Extensions | 49 |

| 5 | Hist | ory     |                                      | 50 |

### 1.1 Erika Enterprise on multicores

Today's embedded systems are continuously being extended to support additional and more complex functionality. In many domains (automotive, telecommunications, domotics), availability of powerful hardware at low prices and cost/time market pressure are pushing for integration of functionality on system-on-chip devices capable of processing large amount of data in a short time.

Multicore systems are being considered as an economically viable alternative to support this increasing computational demand. In this context, Evidence proposes OS-level solutions and tools for embedded multicore-on-a-chip.

The Evidence RT-Druid/Erika Enterprise solution, originally developed for small-scale OSEK/VDX compatible embedded systems for the automotive powertrain market has been ported to the Altera Nios II environment, easing the adoption of reconfigurable FPGA capable of supporting multiple softcores on the same FPGA.

The RT-Druid/Erika Enterprise pair has been designed to handle multicore development and programming by hiding the use of multicore synchronization primitives. With multicore hiding, it is possible to seamlessly migrate application code from a single processor to multicore without changing a single line of the source code.

Hiding helps customers preserving their code base. Retargetting an application from single to multicore architectures only requires different OIL configurations, but allows retaining the same source code in all the configurations.

#### 1.1.1 Systems-On-Chip and FPGAs: the future?

**Trends and challenges from the automotive market.** Electronic components in today's cars are mandatory elements to satisfy tight safety, efficiency and regulation constraints. Current vehicle electronics systems consist of up to 100 embedded controllers connected in a real-time distributed electronic system with several network clusters and electronic control units (ECU). Setup and Management of such complex distributed configurations is now the rapidly becoming the cost, performance and reliability bottleneck of the system. To satisfy tighter cost and packaging constraints the number of ECU should be reduced compared to today cars resulting in an integration of several functions.

To cope with this issue and the related design efficiency, the AUTOSAR [2] industrial initiative is standardizing a common set of hardware and software components and an accommodating platform that allows the integration of applications provided by different sub-system and component makers. This trend and the ever increasing application

complexity (e.g. x-by-wire) demand architectures with multiple computational units.

**FPGAs: the opportunity.** On the silicon technology side, the continuous scaling provides hardware fabrics that allows unprecedented integration of functions in a systemon-chip with very high parallelism. This trend promises that, in the very near future, even the use of reconfigurable hardware and softcores (CPU implemented with FPGAs) will be cost effective for selected applications.

Moreover, several CPU providers (Intel,Motorola, IBM, ARM, etc) have already announced multi-processor platforms with a winning cost/performance trade-off for the consumer and multimedia markets.

The Janus system, developed by ST Microelectronics/Magneti-Marelli Powertrain and Parades, is an example of a single-chip dual-processor platform for power train applications (featuring two 32-bit ARM processors and four memory banks connected by a crossbar switch) offering better cost/performance trade-offs than traditional architectures.

Reconfigurable platforms, such as Altera FPGAs, are providing soft-core solutions like Nios II, offering the opportunity for implementing 4 or more CPUs into even the cheapest Altera Cyclone II chips.

### 1.2 Solving problems when moving code to multicores

The development trends for next generation embedded devices clearly states that the future lies to multicore devices on the same chip. In particular, power management, leak-age power issues, frequency limits, cost reduction and other factors are driving many companies toward the implementation of multicore system-on-a-chip solutions integrating together CPUs, memories, and peripherals.

Altera Nios II is an example of these multicore platforms. Thanks to the configurability of FPGAs, developers can design multicore in minutes. Although on one side hardware design is simplified by tools like Altera SOPCBuilder, on the other side application development is made more complex by the fact that the application code have to be spread out among different processors.

In particular, partitioning the application among the different CPUs, and implementing an efficient communication mechanism between the CPUs are one of the first issues to be addressed at the first stages of the development process. Unfortunately these choices are very critical for later development phases, since changes in the partitioning scheme can heavily change application design.

RT-Druid and Erika Enterprise give support to developers to solve the partitioning issues in multicore applications based on Altera Nios II, enabling the developer to perform code partitioning and then to easily change it at later stages in the design.

#### 1.2.1 Design and programming.

Design and Programming paradigms must exploit the parallelism of these architectures, but programmers are usually not trained for writing code executing in parallel on multiple processors, and designers need to find the best trade-offs for exploiting computing capabilities without incurring in excessive blocking over shared resources or because of synchronization.

With Erika Enterprise, each task can be thought to run on a single processor multi threaded environment. Multicore issues like data cache disabling and mutual exclusion between different CPUs accessing concurrently the same data structures are handled automatically by RT-Druid and Erika Enterprise, simplifying the application design and verification.

#### 1.2.2 Code placement and resource sharing.

The choice of which software has to be placed on which processor is usually called code placement or software binding or partitioning.

The task of the final user is to figure out the right communication pattern(s) / architecture(s) and to implement it. Today's approach used by many development tools is non conclusive, leaving out to the designer the job of choosing the best partitioning and communication scheme for its application, with the risk of making early decisions that may impact heavily on the application code with bad application performance.

In reality, changing the code placement must not impact on the way people design and program applications. The multicore structure must be hided to the user whenever possible, and source code compatibility between mono and multicore, with automatic mapping of application facilities to the new multicore features. This is exactly what the RT-Druid code generator offers, exploiting the multicore support provided by Erika Enterprise.

Future versions of RT-Druid will also enable users to perform well-reasoned partitioning choices integrating the results of timing analysis of the application with schedulability analysis to guide design choices.

#### 1.2.3 Porting of legacy code to new architectures and to multicores.

One of the problems that typically arises when adopting multicores is that application rarely start from scratch with a multicore approach. More often, new applications are upgrades to existing (working) systems that are adapted to particular new environment.

RT-Druid and Erika Enterprise helps porting existing legacy code to multicores because:

- The kernel API is the same for both single and multicore systems.

- A multicore system can be view as an "extension" of a single core. You can add functionality to a system on a separate core, without perturbating too much the application running on the first CPU.

• Application code does not have to be changed when changing the partitioning scheme.

#### 1.2.4 Resource sharing and OS-level mechanisms.

When moving from single processor systems to multicore systems, standard programming paradigms used in real-time systems to access shared resources does not work anymore.

In particular, all the solutions used to avoid the Priority Inversion problem, such as the Immediate Priority Ceiling protocol implemented in the OSEK/VDX standard and in other APIs does not scale to multicores like Altera Nios II.

RT-Druid and Erika Enterprise offer an innovative way to automatically provide support for resource sharing among different processors, automatically integrating resource consistency protocols for multicores when a resource is shared among different CPUs.

### **1.3 Multicore API implementation**

While hardware technology is offering the opportunity for greatly increased performance, conventional RTOS implementations and standards are not yet ready to support multicore architectures. The OSEK/VDX standard for Real-Time Operating Systems has gone a long way in introducing mechanisms for ensuring predictable (schedulable) real-time behavior and has provided the developers of automotive applications with a stable and sound API.

Unfortunately, OSEK/VDX was not meant to be and it is not ready to cope with the challenges posed by a multicore system. In particular, OSEK/VDX fits best on systems where different processors are physically separated and connected through a network (e.g., Flexray, CAN, LIN, etc.), but it does not best fit in systems that implement multicores on the same ECU.

In detail, the OIL configuration language supports the definition of single processor systems possibly communicating using OSEK COM, but provides no support for fundamental multicore issues such as: distribution of the computational activities (tasks) among processors; multicore communication and synchronization; and multicore details hiding for applications compilation and execution.

### 1.3.1 Erika Enterprise and multicore hiding

With multicore hiding - that is the possibility to seamlessly migrate application code from a single processor to multicore without changing the source code - the programmer's view of the application is not compromised, meaning that the RTOS API is supported without changes and only minimal OIL extensions. Furthermore, Erika Enterprise extends the real-time and memory saving features of automotive RTOS to multicore systems.

In detail, Erika Enterprise provides:

- Innovative mechanisms that allow exploiting the main features of Immediate Priority Ceiling in multicore systems.

- Predictable real-time behavior.

- Kernel features and OIL extensions that allow seamless execution of single processor code in multiple processor architectures.

- Tools that support task placement on processors; easy reconfiguration of kernel calls for resource sharing and communication mechanisms from intraprocessor to interprocessor usage.

- Minimal footprint in terms of ROM and RAM usage.

- Real-time performance (such as interrupt and scheduler latencies, and context switch times) in line with the best market options and the possibility of configuring the kernel for constant time O(1) scheduling.

Erika Enterprise hides the multiple processor structure by providing an automatic mapping of the RTOS API calls to the single processor or the multiple processor implementation, according to the target of the call. This mapping is obtained by exploiting an enhanced remote notification mechanism based on multicore interrupts. Remote notification is used to provide an implementation to kernel primitives acting on tasks (resources) allocated to remote processors. Moreover, the notification mechanism is hidden inside the implementation of the Erika Enterpriseprimitives, maintaining the same interface to the developer both for single and for multicore systems.

The additional overhead caused by the remote execution of calls is mainly due to the "send" of the remote notification from one side, and to the interprocessor interrupt that is raised on the receiving side. Most of the overhead of the two calls is due to the internal usage of the Altera Avalon Mutex calls. However, this overhead does not have a great impact on typical applications where remote activations are not as frequent as local activations.

#### 1.3.2 Contention for multicore shared data structures.

In addition to multicore hiding, the mechanisms typically provided by common RTOS for sharing resources with a predictable and bounded blocking time, such as the Immediate Priority Ceiling protocol and the often related mechanisms for sharing stack space among application tasks lose some of their hard real-time properties (such as predictable blocking times).

Erika Enterprise implements an advanced protocol used when sharing resources among tasks allocated to different processors. The protocol, known as Multicore Stack Resource Policy (MSRP), makes internal use of spin-locks among different processors to ensure data consistency.

We expect that contention for multicore shared resources among different systems will be the main source of overhead in the system. To reduce them, critical section for multicore shared data structures should be reduced as much as possible, for example making local copies of the data structures when possible.

### 1.4 Erika Enterprise for the Altera NIOS II platform

This document describes the details of the Erika Enterprise porting for the Altera Nios II platform. Altera Nios II is a powerful soft-core processor, which is basically a 32-bit RISC microcontroller especially designed for the Altera FPGAs which can be customized to meet high performance or low hardware (in terms of Logic Elements) requirements. The Altera Nios II core can also be highly customized adding custom peripherals, custom assembler instructions, debug features, caches, and other features.

As you will note by reading the following pages, Erika Enterprise fully supports the various features of the Nios II platform, maintaining the Altera workflow based on Quartus II, SOPCBuilder, and Nios II IDE.

Erika Enterprise runs on every typical single core Nios II design without requiring any modification to the hardware. All the Nios II HAL functions, drivers, and features are retained on a Erika Enterprise system.

On the other hand, Erika Enterprise shows its performance and its ease of use when the designer moves from simple single CPU Nios II designs to more complex multicore Nios II designs. In particular, Erika Enterprise has been designed to address in a simple way all the problems that can arise when dealing with multicore systems.

Designing multicore System-on-a-chip (SOC) has always been a difficult task, because it involves a deep knowledge of hardware details and application details that are needed to perform a correct co-design between the application parts that have to be implemented in hardware, and those that have to be implemented in software. Moreover, in a multicore system, the user have to understand how the various software functionality maps to the available computational resources, in a way to optimize the system performance. Choosing the right partitioning scheme for a multicore system is one of the most difficult tasks, because a wrong application partition heavily impact on application performance and response times. In fact, tuning a multicore design is usually made in various design steps. Each design step in fact refers to different stages in the application design, and often the result is a tradeoff with the design choices that were made earlier in the application definition.

The design tools provided by Altera allow designers to easily create and test multicore hardware platforms based on the Altera Nios II Processor. Basically the developer creates a multicore platform by simply inserting CPUs and connecting peripherals using the Altera SOPCBuilder Tool. Using this tool the designer can modify the hardware architecture easily, adding and removing CPUs, modifying the bus connections, and so on. Once the hardware platform has been created and generated, the developer can develop the software separately for each CPU using the Nios II IDE based on Eclipse. Altera provides a nice environment where for each CPU the user can instantiate the device drivers of the hardware components connected to the particular CPU (using the provided Altera HAL and the System Libraries Projects). After that, the user can create

a C/C++ application that is linked to a single System Library (that is, to a single CPU).

It is our believe that the common workflow during the design of complex multicore applications requires a frequent number of change in the partitioning of the software among the different CPUs. That is typically needed because application requirements often change during the development of an embedded system, and the choices that has been made earlier in the design may not be the right ones at the end of the development. In this sense, the developer must have the power to change the software partitioning among processors with little effort, as it is currently done for the hardware part in SOPCBuilder, where the user can change the hardware configurations with a few mouse clicks.

That is exactly what Evidence Srl aims to provide to Altera Nios II customers: a way to simply deal with the complexity of multicore software development, easing the partitioning of applications on different processors, giving the possibility to developers to change their partitioning without changing their source code.

Briefly, Evidence Srl provides a powerful design and configuration tool named RT-Druid, and an RTOS, named Erika Enterprise. The RT-Druid Toolset and Erika Enterprise RTOS exploit the multicore capabilities of the Altera FPGA boards and allow to fully use the power of the multicore designs.

On the host side, RT-Druid offers an integrated view of a multicore application under the Nios II IDE, allowing the user to partition the application jobs on the different available CPU. To do that, RT-Druid offers a concept of "application" project that spans different CPUs, allowing an easy move of features across the execution units. RT-Druid is a set of plugins for the Eclipse framework that are integrated with the Altera Nios II IDE, giving the possibility to the user to:

- develop a multicore application using an RT-Druid project, that is an Eclipse Project that is able to handle the software for all the CPUs in the multicore system<sup>1</sup>;

- specify one or more partitioning schemes to be used for a multicore system;

- generate the configuration code for the Erika Enterprise RTOS;

- analyze the results of the partitioning using schedulability analysis<sup>2</sup>;

On the target side, Erika Enterprise offers a multiprogramming environment that can be used to deploy the application architecture defined in RT-Druid on the real hardware. Erika Enterprise helps the partitioning job supporting code deployment that is independent from the particular CPU, allowing the use to move code between CPUs without changing it. Erika Enterprise is a Real-Time Operating System (RTOS) that offers a multicore partitioned multithread environment that internally takes care of multicore issues like activation and run of remote tasks, periodic alarms, and shared resources among

<sup>&</sup>lt;sup>1</sup>A single **RT-Druid** Project can be viewed as a replacement for the set of Altera Application Projects for each CPU.

<sup>&</sup>lt;sup>2</sup>The schedulability analysis plugin will be available together with the next version of RT-Druid

tasks allocated to different processors. Of course, as said before, the restriction to single processor designs is supported. Erika Enterprise currently offers support for fixed priority scheduling, with preemptive, non preemptive and mixed preemption support.

$\mathsf{Erika}\ \mathsf{Enterprise}$  is ready for formal compliancy with the OSEK/VDX operating system standard.

The main feature in the Evidence approach for Nios II is the fact that the RT-Druid Toolset and Erika Enterprise do not change the current Altera Workflow. For that reason, users accustomed with the Nios II IDE editing and debugging features can easily reuse their knowledge.

Some of the features supported by RT-Druid and Erika Enterprise are:

- Support for the definition, and deployment of software for Nios II multicore systems with shared memory.

- Support for partitioning of the application functionalities on different processors with negligible modification to the source code base.

- Support for easy change of the partitioning scheme allowing the developer to easily try and test different partitioning schemes.

- Support for the migration of single processor source code to multicore systems.

- Support for the Altera development toolchain: RT-Druid and Erika Enterprise are perfectly integrated with Altera Nios II, reducing the learning curve of the tools.

Specific Altera integration features include:

- Integrated as a component in the Altera HAL;

- Compatible with the Altera HAL peripheral drivers and system libraries;

- Support for nested interrupts;

- Support for a RTOS configuration code generator compliant with the OSEK OIL specifications;

Moreover, the multicore support of Erika Enterprise includes:

- Advanced software partitioning support:

- developers can decide which task goes on which processor;

- developers can move tasks between processors without changing the source code;

- Transparent handling of shared resource locks behavior depending on the partitioning of the application;

- Interprocessor interrupt support;

- Shared resource support using queuing spin locks on top of the Altera Mutex Peripheral;

- Automatic cache disabling technique without changes to the user source code (only changes to data definitions);

- Support for multicore scheduling algorithms with bounded blocking times on multicore;

The following chapters describe in detail the single and multicore support for the Altera Nios II platform that is offered by Erika Enterprise and by RT-Druid, highlighting the various features available and the main architecture design requirements of the system.

## 2 Single CPU designs

The purpose of this chapter is to describe in detail the single CPU design support that is offered by Erika Enterprise and by RT-Druid, highlighting the various features available to the Altera developers.

### 2.1 Single core Design Flow

The purpose of this section is to shortly describe the design flow that must be used to develop a single core system using the tools provided by Altera and by Evidence Srl. As it can be seen, the design flow is equivalent to the current Altera design flow.

The first step of a Nios II single core system is the hardware design. Every hardware design which is able to run the Altera HAL can also run Erika Enterprise. For example, the standard, full\_featured, ... designs provided by Altera for the various evaluation boards can be used as a starting point by the designer.

Once the hardware design has been defined, the designer can develop the application software using Altera Nios II IDE (based on the Eclipse Framework).

Using Nios II IDE the designer have to instantiate an Altera System Library Project for each CPU in the system. The Altera System Library contains the device drivers for the peripherals that are actually connected to the CPU the library refers to. Please refer to the Altera documentation on how to create a System Library.

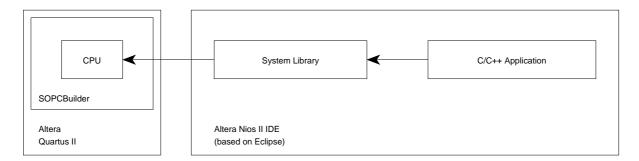

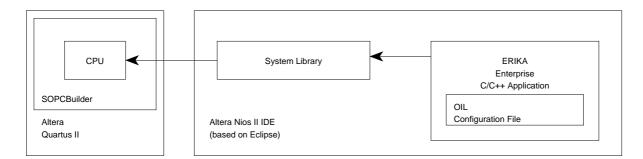

After creating an Altera System Library for each CPU, the designer can create an RT-Druid Project. The RT-Druid Project contains the application that will run on the Nios II processor, and it is similar to the "C/C++ Application" project provided by Altera. As it will be described later, the only difference with the Altera project is that the configuration of the system is defined inside a text file which follows the OSEK OIL specification [1]. Figure 2.1 and 2.2 graphically shows the difference between the Altera and the Evidence approach: the Altera HAL approach provides a C/C++ application project for each CPU, whereas Erika Enterprise provides a RT-Druid project. RT-Druid Projects are described in Section 3.2, and in the RT-Druid Reference Manual.

Then, the designer compiles the application to create a set of compiled files that are equivalent to the files generated by the normal Altera Projects makefiles. As a result, the developer can debug the application in the same way as all the other Altera HAL applications.

### 2.2 Altera System libraries

Erika Enterprise uses the same System Libraries that are provided together with the

Figure 2.1: This Figure displays the Altera approach to software development for single core Nios II designs. Each Application is linked to a System Library which contains the peripherals instantiated in SOPCBuilder for the CPU.

Figure 2.2: This Figure displays the Evidence Srl approach to software development for single core Nios II designs. Each RT-Druid Project contains an OIL configuration file that specifies the application and kernel configuration. The RT-Druid Project is linked to a System Library which contains the peripherals instantiated in SOPCBuilder for the CPU. Altera HAL. When using the Altera System Libraries, developers have to take care of the following issues:

- One System Library has to be created for each CPU in the system.

- Separate stack space for exceptions should not be set inside the System Library properties. A similar feature can be obtained by setting a separate interrupt stack inside the OIL configuration file.

- Custom linker scripts are supported with Erika Enterprise. Custom linker scripts can be specified inside the System Library project properties.

### 2.3 Using Interrupt handlers with Erika Enterprise

Users of the Altera HAL can continue to use the Altera provided functions for interrupt handling. In particular, alt\_irq\_register() must be used to provide the registration of an interrupt handler. alt\_irq\_interruptible() and alt\_irq\_noninterrtptible() must be used to handle interrupt nesting.

The Nios II Erika Enterprise implementation considers all the interrupt handlers as interrupts of category 2. Erika Enterprise correctly handles interrupt nesting, performing appropriate checks at the end of the last interrupt to implement task preemption. There is no support for Interrupts of Category 1 in Nios II because of the internal structure of the Nios II processor.

Among the options available on the Altera System Library Properties, there is one named *Use a separate exception stack*, that can be used to allow interrupts and exceptions stack to be allocated in separate memories. This feature is typically used to move the interrupt stack in faster memories, such as on-chip tightly coupled memories. When developing applications using Erika Enterprise, the separate stack as specified in the Altera System Library cannot be used. A similar feature can be obtained with a multistack configuration of Erika Enterprise.

### 2.4 The StartOS function

To start the multiprogramming environment the designer have to call the StartOS() function inside main() or alt\_main().

The StartOS() primitive does the following actions:

- 1. It registers the interprocessor interrupt routine and initializes the Altera Mutex Peripheral.

- 2. It implements the startup barrier (only on a multicore system).

- 3. It calls StartupHook.

- 4. It activates autostart tasks and alarms.

#### 2 Single CPU designs

| Preferences                |                                                                                                                         |                       |  |  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|

| type filter text           | Nios II                                                                                                                 | (+ <del>+</del> )     |  |  |

| General     C/C++     Help | Set global Nios II build and run settings.<br>There should rarely be a reason to change these preferences from the defa |                       |  |  |

| install/Update             | Show command lines when running 'make' (i.e. Don't use '-s' flag on make)                                               |                       |  |  |

| Nios II                    | Generate objdump file                                                                                                   |                       |  |  |

| Rt-Druid                   | Allow multiple active run/debug sessions                                                                                |                       |  |  |

| Run/Debug                  | Confirm before starting the flash programmer                                                                            |                       |  |  |

| 👜 Team                     | Warn about launches in Run mode for C/C++ Application projects usin                                                     | ig Host-based File Sy |  |  |

|                            | Restore D                                                                                                               | refaults Apply        |  |  |

| 0                          | ОК                                                                                                                      | Cancel                |  |  |

- Figure 2.3: Nios 2 IDE preference window. The "Allow multiple runs" checkbox must be checked.

- 5. It checks for preemption.

- 6. It returns to the caller.

Please note that StartOS() returns to the caller only when the system have an idle time, that is, when all the task activations has run.

The code literally after StartOS() must correspond to background activities that does not use Erika Enterprise services.

If unsure of the code that have to be put after the call to StartOS(), use the following forever loop:

for (;;);

### 2.5 Altera Nios II IDE tips and tricks

This is a list of the preferences of the Altera Nios II IDE that needs a modification:

- Allow multiple active runs. This option can be found in "window/preferences/nios2/ allow multiple active runs". You need to set this option to be able to debug multicore systems (see Figure 2.3)

- **Build if required** This option can be found in "window/preferences/rundebug/launching/build if required". This option can be used disable the application automatic build (see Figure 2.4. Since building a multicore system may require a lot of time, this options waiting time when avoids automatic building when the user has to start different debug sessions without need of recompiling the system.

#### 2 Single CPU designs

| type filter text                                                                  | Launching 🔅 🕶 🛁                                                                                                                                                        |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ⊞ General<br>⊞ C/C++<br>⊞ Help                                                    | Save required dirty editors before launching<br>Always Never ® Prompt                                                                                                  |

| Install/Update     Nios II     Rt-Druid                                           | Wait for ongoing build to complete before launching<br>Always     Never      Prompt                                                                                    |

| Run/Debug<br>Console                                                              | Launch in debug mode when workspace contains breakpoints <ul> <li>Always</li> <li>Never</li> <li>Prompt</li> </ul>                                                     |

|                                                                                   | Continue launch if project contains errors<br>O Always  Prompt                                                                                                         |

| - Perspectives<br>- String Substitution<br>- Trace<br>- View Management<br>- Team | General Options<br>V Buld (fr required) before launching<br>Remove terminated launches when a new launch is created<br>Size of recently launched applications list: 10 |

| <                                                                                 | Restore Defaults Apply                                                                                                                                                 |

| 0                                                                                 | OK Cancel                                                                                                                                                              |

Figure 2.4: Nios 2 IDE preference Run/Debug window. Consider unchecking the "Build if Required" checkbox.

## 2.6 Usage of the Altera HAL device drivers with Erika Enterprise

Erika Enterprise currently does not provide any customized versions of the Altera HAL device drivers.

In general, the Altera HAL device drivers have to be used with care in multitask application developed with Erika Enterprise, because these device drivers are designed for a single task environment.

In particular, some care have to be taken avoiding that more than one task calls a device driver set of primitives concurrently. There are two possibilities:

- Allocate a dedicated task that is the only one that uses a given device driver primitive (for example, if a CPU has a JTAG UART, the user should allocate a single task that is responsible for the standard input/standard output operations on that peripheral).

- Allow different tasks to use the primitives in a mutual exclusive way. In that case, mutual exclusion can be obtained using a Resource dedicated to the purpose, and using GetResource and ReleaseResource primitives to sequentialize the accesses to the shared resource.

In general, all the file system primitives that are potentially blocking on a system are implemented with a busy wait within the HAL. For that reason, use these primitives in non-blocking mode. Future versions of Erika Enterprise will include a customization of the Altera HAL drivers to allow file system primitives to become blocking primitives.

The purpose of this chapter is to describe in detail the multicore support that is offered by Erika Enterprise and by RT-Druid, highlighting the various features available.

### 3.1 Multicore Design Flow

The purpose of this section is to shortly describe the design flow that must be used to develop a multicore system using the tools provided by Altera and by Evidence Srl. As it can be seen, the design flow is equivalent to the current Altera design flow, with some additional points that are needed to create Erika Enterprise compatible hardware and software.

The first step of a Nios II multicore system is the multicore hardware. A multicore hardware can be obtained easily using Altera SOPCBuilder, as described in the document named "The Multiprocessor Nios II Systems Tutorial" [3] that describes the basics of designing a multicore Nios II system. Please refer to that document for the basic informations on how to create a generic Nios II multicore hardware.

Multicore designs compatible with Erika Enterprise can be built starting from the standard peripherals provided by Altera. For a multicore design to be compatible with Erika Enterprise, special care have to be taken when instantiating particular Altera peripherals and memories. Please refer to the following sections for the guidelines to be followed when adding the following hardware features:

- Interprocessor Interrupt (see Section 3.7);

- Altera Avalon Mutex (see Section 3.5);

- Memories (see Section 3.4);

A step-by-step description on how to create a multicore hardware is also available inside the "ERIKA Enterprise Multicore Tutorial for the Nios II hardware", available for download at the Evidence web site.

Once the hardware design has been defined, the designer can develop the application software using Altera Nios II IDE (based on the Eclipse Framework).

For each CPU in the system, the designerhave to instantiate an Altera System Library Project. Please refer to "The Multiprocessor Nios II Systems Tutorial" [3] for details.

After creating an Altera System Library for each CPU, the designer can create an RT-Druid Project. The RT-Druid Project contains the application that will run on *all* processors of the system. In a way similar to the single CPU designs for Erika Enterprise, the RT-Druid Project contains an OIL configuration file. The OIL file [1] specifies the

partitioning scheme adopted by a particular application. RT-Druid Projects are described in Section 3.2.

Next, the designer compiles the application to create a set of compiled files that are equivalent to the files generated by the normal Altera Projects makefiles. As a result, the developer can debug the multicore application as usual using an Altera Multiprocessor Collection. Please refer to "The Multiprocessor Nios II Systems Tutorial" [3] for details.

### 3.2 Basic notions for multicore programming

This Section is a simple list of definitions and general terms that highlight characteristics of the systems that can be designed using RT-Druid and Erika Enterprise.

**A single SOPCBuilder Block.** Multicore systems handled by Erika Enterprise are defined inside a single SOPCBuilder block. This is somehow similar to the approach followed by "The Multiprocessor Nios II Systems Tutorial" [3].

**Partitioning of tasks and data on multicores.** When developing a multicore system, the user have to think as the application as a whole. The application will be composed by a set of tasks, shared resources, that will work cooperatively to reach the application goals. The approach chosen by Erika Enterprise is a so called *partitioning* approach, that is, each concurrent task is statically linked at build time to a given CPU. Each CPU includes a separate copy of the operating system and of the device drivers that are present on the particular CPU.

Tasks partitioning into CPUs can be done at the end of the application design: the configuration system is in fact designed in a way to allow the designer to write partitioningindependent code; then, the developer can change the CPU partitions without changing the application source code, giving the possibility to really exploit the power of Nios II multicores.

The minimal partitioning item in a system is the source file. That is, the code of tasks allocated to different CPUs are typically put by designers on different files, to allow an easy partitioning in different CPU in a later stage of the development.

**CPUs are not identical.** There are various differences between the different CPUs in a SOPCBuilder Block. First of all, they may come from different versions of the Nios II core, with possibly different custom instructions. Moreover, Nios II peripherals are typically connected to a single CPU<sup>1</sup>, and that means that each CPU will have a different set of interrupts, memories, and software device drivers.

**The Master CPU.** There is a  $CPU^2$  which plays an important role in the system. That CPU is usually called *Master CPU* and is referred in the source code as MASTER\_CPU.

<sup>&</sup>lt;sup>1</sup>With the exception of the Altera Avalon Mutex Peripheral

<sup>&</sup>lt;sup>2</sup>With Nios II 5.0 and 5.1, it was the CPU with CPUID equal to 0, that wast typically the first CPU in the SOPCBuilder CPU list.

In multicore systems supported by Erika Enterprise, the Master CPU plays an important role, because it acts as the CPU that have to initialize the shared data (see Section 3.4 and, if configured, the startup barrier (see Section 3.6).

The Master CPU is specified in the OIL configuration file as described in the following example, where cpu0 is specified as the Master CPU:

```

CPU test_application {

OS EE {

...

MASTER_CPU = "cpu0";

CPU_DATA = NIOSII {

ID = "cpu0";

...

};

...

};

```

Altera mutexes. The multicore system must include at least an Altera Avalon Mutex peripheral. That peripheral will be handled internally by Erika Enterprise to guarantee mutual exclusion between different activities residing on different CPUs (see Section 3.5). The application does not use directly the mutex peripheral. If a startup barrier is configured, a proper initialization value for the mutex have to be selected (see Section 3.6).

**Multicore Interrupts.** The multicore system must include a Multicore Interrupt feature. When developing a multicore application, the designer have only to think at the existence of concurrent tasks that will be activated and scheduled on the different CPUs. Erika Enterprise hides the implementation details to the developer, and the developer does not have to handle the multicore communication issues. Internally, Erika Enterprise uses a Multicore Interrupt hardware support, that is used to dispatch various information between the various CPUs. The instantiation of an Interprocessor Interrupt peripheral is done connecting together a set of Altera Avalon PIO components in SOPCBuilder (see Section 3.7 on how to instantiate a proper Multicore Interrupt controller).

**Shared Memories.** A multicore system typically includes some shared memory (that can be on-chip or off-chip). Shared memories will be used to exchange informations between the different CPUs. The main idea is that the designer has the option of defining data structures that are global and visible to all cores. Moreover, all the CPUs will access the data structures using an automatic cache disabling technique without changing the application source code<sup>3</sup>. This kind of shared data structures will be defined inside the Master CPU.

Moreover, the designer can define a shared data structure leaving RT-Druid the choice if that data structure should be local to a CPU or global to all the CPUs in the system.

<sup>&</sup>lt;sup>3</sup>Please remember that Altera Nios II does not have a cache coherency mechanism.

The rationale behind this is that local shared data structures are more efficient than global data structures, and also the fact that a shared data structure must be local to a CPU or global depends on the partitioning that the designer defines for the application. Leaving the choice to RT-Druid allows designer to write partitioning independent code. See Section 3.4 for details.

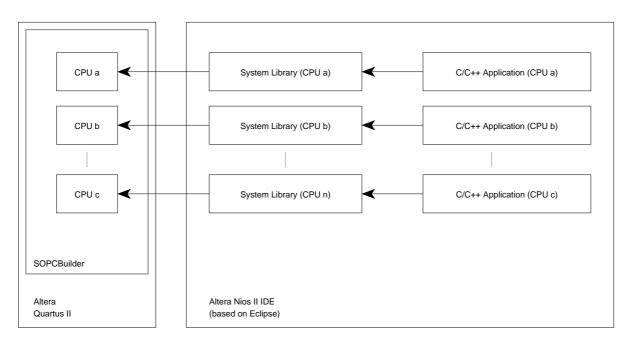

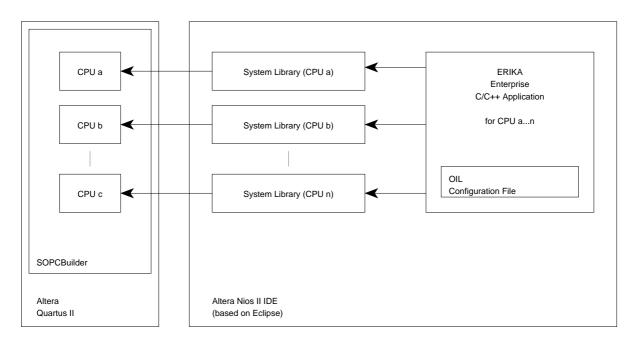

RT-Druid **project and Altera System Libraries.** The Nios II IDE project layout for an Erika Enterprise Application slightly differ from the Altera counterpart. In particular, the user has to instantiate a Nios II IDE system library for each CPU. Erika Enterprise allows users to reuse all their preexisting source code developed for the Altera HAL, adding multiprogramming support to ease the partitioning job and to fully utilize the multicore power available with Altera Nios II. Then, the user application is set up inside a RT-Druid Project. An RT-Druid Project is similar to an Altera C/C++ Application Project, except that an RT-Druid Project includes the application software for all the CPUs. The partitioning of the application tasks to processors is specified using a configuration file written following the OSEK OIL Standard [1]. The result of the compilation is an ELF file for each CPU, that can be processed in the same way as the ones produced by normal Altera Nios II Projects. When compiling an RT-Druid project, Figure 3.1 and 3.2 graphically shows the differences between the various versions: the Altera HAL approach provides a C/C++ application project for each CPU, whereas Erika Enterprise has only one project (the RT-Druid project) for all the CPUs. Please refer to the RT-Druid manual on how to create a new RT-Druid Project.

### 3.3 Data scopes in an Erika Enterprise multicore system

Data allocation in multicore systems based on the Nios II processor are a little bit different than conventional single processor architectures. In particular, a C data definition may be classified in one of the following points.

**Automatic data**. These data are allocated on the current stack by a function call when the function is called. The scope of these data is the function itself. Example:

```

void foobar(void)

{

int this_is_automatic;

...

}

```

**Static data**. Static data is a C global variable that is defined as static. Only the source code inside a file that define the static variable can refer to the particular symbol. Example:

```

static int this_is_static;

```

Figure 3.1: This Figure displays the Altera approach to software development with multicore Nios II designs. In particular, there is one Application for each CPU. each application is linked to a System Library project, which is linked to the CPU instantiated in SOPCBuilder.

**Global data**. Global data are C global symbols. The scope of these symbols is the entire source code that is linked inside an ELF file. That is, global data is **not** shared among different CPUs. Global data is also called *Local data* (to emphasize the fact that they are allocated to a single CPU only).

int this\_is\_global;

**Heap.** Heap data structure are region of memory that are allocated dynamically using library functions such as malloc() and free(). Typically, each processor has its own private heap memory pool, that each processor handles independently using a local copy of the above mentioned Standard C library functions.

Application data structures allocated in the heap typically are local to each processor and should not be shared among different processors. Erika Enterprise does not give any explicit support to share a heap variable (typically a pointer) between tasks allocated to different processors. To do that, the developer must ensure that:

- the heap memory resides on a memory zone accessible by the different processors that access it;

- proper cache disabling strategies are used to ensure that each processor uses the data consistently;

Figure 3.2: This Figure displays the Evidence Srl approach to software development with Nios II IDE. In particular, there is only a single application for every CPU, contained inside the RT-Druid Project. The RT-Druid project contains the Application partitioning and the kernel configuration inside the OIL file. In this sense, the single CPU case showed in Figure 2.2 is a special case of this Figure. Then, each CPU has its own System Library, which is linked to the CPU instantiated in SPCBuilder. • the memory is allocated and freed on the same processor (that is, the developer cannot allocate a data structure on CPU *a* and free it on CPU *b*, because it would have called two different independent allocators, the allocator on CPU *a*, and the allocator on CPU *b*).

**Multicore global data.** Multicore global data are data structures that are visible to all CPUs in the system. This kind of data structure does not exist on a single processor system. These data structures are typically defined and initialized inside the Master CPU, and the are accessible to all the other CPU.

The Multicore Global data must be accessible to all the CPUs, that is, it must reside on a memory accessible to all the CPUs. As an alternative, the user can let the memory be shared among the CPUs that really uses the shared memory, plus the Master CPU (This may help saving some LE reducing the arbitration logic). Multicore global data not shared by the Master CPU is not supported in this release of Erika Enterprise (but will probably be supported in future releases).

When a CPU access a multicore global data, the data cache, if present, is automatically disabled<sup>4</sup>.

**Stack.** The stack memory is used to store function calls, return address, and parameters. Each task in **Erika Enterprise** has a stack, that may be shared with other threads to reduce the overall stack space required by an application.

Basically, each CPU has stack called "shared", that is a fixed size amount that can be specified in the OIL configuration file. The shared stack has its top at the top of stack specified for each CPU inside the Altera System Library. That is, the main() function is always run on the shared stack (that is the same behavior of normal Altera HAL applications.

Additionally, each task in the system can have a private stack. A private stack is always needed if the task use blocking primitives like, for example, WaitEvent. Private stacks are allocated on the same CPU where the task is allocated.

### 3.4 Memory types and their allocation

Altera SOPCBuilder provides the user different kinds of memory types, ranging from onchip tightly coupled memories, onchip memories, and external SRAM, SDRAM and Flash memories.

All these different kind of memories can be used to store data and code. To let the content of a memory being shared among tasks allocated to different processors, the the memory slave ports must be connected to all the CPUs that access them.

In general, we will consider a system composed by a set of CPUs that have some "private" memory components (connected to that CPU only), and a set of "shared memory" components (connected to all the CPUs).

<sup>&</sup>lt;sup>4</sup>Without the need of changing the source code, using bit-31 cache disabling.

In the following, we will consider that the shared memories are connected to all the available CPUs. Having memories connected to all the CPUs has the following draw-backs:

- If a CPU does not need any data structure allocated on a particular memory component, the connection logic used to connect that CPU to the memory component is wasted. In any case, unused arbitration logic can be removed in the final product if needed.

- Having a fully connected memory helps partitioning tasks to different processors without changing the hardware. That is especially helpful at design phase, where task partitioning is not definitive.

- Fully connected memories, allows a proper handling of the system startup. The idea is that the Master CPU have a role of "container" and "allocator" of all the shared data structures in the system. All the definitions of the shared data structures are done in the Master CPU. Having a single CPU responsible for the allocation of the shared data structures simplifies the system architecture because the linker takes care of allocating shared data structures to separate addresses.

In this way, Erika Enterprise frees the designer the need to manually allocate shared data structures to separate memory zones, that at the end forces the developer to manually implement the linker job.

Using fully connected memories has the additional advantage of automatically adapting to partitioning changes, because inserting new shared data structures (for example because the designer splits a task in two parts allocated to different processors), or removing existing multicore shared data structures (because using proper partitioning data structures that were multicore global may become local when all the tasks accessing it are allocated on the same CPU) is handled *automatically* by RT-Druid and Erika Enterprise, without requiring any kind of manual configuration or, worse, hardware change.

Please note that whether for simple applications partitioning code and data structures is a human manageable task, when the application size grows the complexity of the configuration may be source of human errors and inefficiencies, especially if the development requires partitioning changes during system development.

The approach proposed by RT-Druid and Erika Enterprise allows a simple way to manage the partitioning problem, helping the designer concentrating on the application architecture instead of concentrating on the communication support of the application. After the application is developed, the partitioning will also influence the kind of communication pattern used to access the data structures. All that is done only at the software level, without modifying the hardware.

Memory allocation for the application data structures works as follows:

• The developer defines its data structure. See Section 3.8 on how to define a multicore shared data structure; see Section 3.8.4 about a discussion on GP-relative addressing for multicore global data.

- The linker allocates the data structures into memory sections, that are then located inside the memory components available in the hardware. The available memory sections are typically found in the Altera generated linker script in the System Library of each CPU<sup>5</sup>.

- The only requirement that have to be fulfilled in this phase is that multicore global data structures must be allocated in memories that are connected to the various CPUs that may access the data. Since memories offsets in the address space are common to all the CPUs, pointers and addresses can be shared freely.

There is no restriction in the allocation of local variables (except the obvious one that variables local to a CPU must be allocated in a memory space that is accessible by that CPU). Of course, local variables should be allocated in preference to private memories.

Note: when the RT-Druid Code Generator generates the Erika Enterprise configuration code for a multicore system, some multicore shared data structures are generated. By default, these data structures are allocated inside the .rodata, .sdata and .data section of the Master CPU. As an alternative, a different memory region for the code generated by RT-Druid can be selected by specyfying the MP\_SHARED\_RAM and MP\_SHARED\_ROM attributes in the OIL file. The following example shows how the code generated by RT-Druid can be allocated on two memories .myram and .myrom:

```

CPU test_application {

OS EE {

MP_SHARED_RAM = "__attribute__ ((section (".myram")))";

MP_SHARED_ROM = "__attribute__ ((section (".myrom")))";

...

};

...

};

```

• Since the allocation of multicore data is done automatically by the linker, the design of a multicore system should take care of the fact that more than one CPU can access the same memory component at the same time for data that may be uncorrelated. That is, the bandwidth of the memory component is shared between different tasks that may access multicore global data structures that are not correlated, eventually creating bottlenecks. Such situations can be prevented by appropriately fragmenting memory components if possible, allowing decoupled parallel access to the different banks (for example, instead of having a big onchip memory of 64Kb, having 2 32k memories with an appropriate partition of the data structures).

<sup>&</sup>lt;sup>5</sup>Note that developers may specify their own custom linker script.

### 3.5 Handling data consistency using mutual exclusion

Whenever a data structure can be accessed concurrently by different tasks, a mutual exclusion mechanism must be used to ensure that the shared data structure is accessed without consistency problems.

Erika Enterprise provides a mutual exclusion mechanism between concurrent tasks through the abstraction of Resource. Resources are similar to binary semaphores, and can be locked using the GetResource primitive and released using the ReleaseResource primitive.

A Resource is modeled using an Erika Enterprise Resource object, that can be thought as a binary semaphore plus a rule that says that when a task  $\alpha$  allocated on a CPU tries to lock a resource locked by another task  $\beta$  on another CPU, then  $\alpha$  actively spins waiting for  $\beta$  to release the lock. This protocol is also called Multiprocessor Stack Resource Policy (MSRP)

These primitives can be used by tasks independently from the CPU where the tasks are allocated to. The RT-Druid Code Generator, and the implementation of the primitives done on Erika Enterprise, guarantees that GetResource and ReleaseResource can be transparently remapped to multicore platform, hiding the complexity of the multicore platform.

Basically, the RT-Druid Code Generator handles in a different way Resources that are used only by task allocated to the same CPU (*local* resources ) and Resources that are used by tasks allocated to different CPUs (*global* resources ).

Locking a local resource only provoke a modification in the scheduling parameters on the local CPU, whereas locking global resources involve a coordination between tasks allocated to different CPUs that is solved by the Erika Enterprise using an Altera Avalon Mutex peripheral internally.

The kind of lock implementation used for a particular resource only depends on the partitioning defined in the OIL file. Please note that developers does not have to modify their code after a system repartitioning that changes a resource from local to global or vice versa.

The options that influence Resources and their allocation in the OIL configuration file are described in the following example:

```

CPU test_application {

OS EE {

NIOS2_MUTEX_BASE = "MUTEX_BASE";

...

};

TASK thread0 {

CPU_ID = "cpu0";

RESOURCE = myresource;

...

};

```

```

RESOURCE myresource {

RESOURCEPROPERTY = STANDARD { APP_SRC = "resourcedata.c"; };

};

...

};

```

Basically, the developer have to specify inside the property NIOS2\_MUTEX\_BASE the base address that is generated by the system library inside the system.h file. The name of the base address is typically the name used in SOPCBuilder (uppercase), plus the suffix \_BASE. For example, for a mutex device called mutex, then the name of the base address to be used is MUTEX\_BASE. Then each thread have to declare the resources it use. Finally, the Resource have to be declared, eventually specifying additional source files. When generating the configuration code, if the Resource will be local, these source files will be linked to the CPU where the tasks that use it are allocated; otherwise, the source files will be linked together with the Master CPU.

Please note that (starting from Nios II 6.0, the Erika Enterprise implementation does no more use the HAL mutex driver, but it uses its own mutex driver.

### 3.6 Startup barrier

Each processor in a multicore environment is characterized by a different set of peripherals, a different size of code and data structures. As a drawback, each CPU will have a different startup code implying that each CPU will have a different boot time (let's consider the boot time the time from the CPU reset to the execution of the first assembler instruction of the main() function).

Since the different CPUs will execute a set of interacting code, it is important that all the CPU execution will be synchronized before they start the application, giving in that way the time to all the CPUs to startup their peripherals, and to properly initialize their global data structures. We call that initial synchronization a "startup barrier".

Erika Enterprise provides an (optional) startup barrier service. When configured and correctly used, the CPUs will run the boot code, and will stop at a synchronization point inside the StartOS() primitive until all the CPUs have passed it.

The implementation of the startup barrier uses the services of the Altera Avalon Mutex peripheral. In particular, to implement the startup barrier we used the *Initial Owner* feature as shown in Figure 3.3.

The settings to be used when configuring the startup barrier are the following:

• The Altera Avalon Mutex initialization values are set according to Figure 3.3. Please note that if you are using Nios II version 6.0, the value 0 is set in any case and it has no relationship with the CPUID register values assigned by SOPCBuilder<sup>6</sup>.

$<sup>^{6}\</sup>mathrm{If}$  you are using Nios II versions 5.0 and 5.1, 0 is the CPUID register value for the first CPU.

| 4 Mutex - mutex                                                                                         |                     |                 |  |  |

|---------------------------------------------------------------------------------------------------------|---------------------|-----------------|--|--|

| MegaCore'                                                                                               | Mutex               | Documentation   |  |  |

| Parameter<br>Settings                                                                                   |                     |                 |  |  |

| ⊂Initial setting                                                                                        | js                  |                 |  |  |

| Initial value:                                                                                          | 0×1                 |                 |  |  |

| The initial value must be between 0x0 and 0xFFFF.<br>Set to a non-zero value to allow an initial owner. |                     |                 |  |  |

| Initial owner:                                                                                          | 0×0                 |                 |  |  |

| The initial ow                                                                                          | ner must be between | 0x0 and 0xFFFF. |  |  |

| Info: The initial owner must release the mutex before it can                                            |                     |                 |  |  |

| •                                                                                                       |                     | Þ               |  |  |

|                                                                                                         |                     | Cancel Finish   |  |  |

Figure 3.3: This Figure displays the *Initial Value* and the *Initial Owner* setup for the Altera Avalon Mutex peripheral. The setting must be different from 0 only when using the startup barrier feature.

- The first cpu that is listed in the OIL file is the first CPU that is listed in SOPCBuilder (in this way, RT-Druid will assign that CPU the index 0.

- The Master CPU setting in the OIL file is set to the first CPU, and the STARTUPSYNC value is set to TRUE as shown below:

```

CPU test_application {

OS EE {

MASTER_CPU = "cpu0";

CPU_DATA = NIOSII {

ID = "cpu0";

...

};

CPU_DATA = NIOSII {

ID = "cpu1";

...

};

STARTUPSYNC = TRUE;

...

};

```

If you want not to configure the startup barrier, you have to set all the initialization values of the Altera Avalon mutex to 0, and the STARTUPSYNC value to FALSE<sup>7</sup>.

Warning: If you are using Nios II 5.0 or 5.1, please read the following paragraphs. Please note that unfortunately Altera does not guarantee an assignment pattern to the CPUID (ctr15) values. The CPUID values are assigned in an automatic way by SOPCBuilder, and the user does not have control over it. For that reason, the value that is set as initialization value for the Altera Avalon Mutex may be not what the user would like to. In our experiments, we found that an initialization value of 0 typically corresponded to the first CPU in SOPCBuilder, but unfortunately there is nothing that really specifies the assignment strategy of CPUIDs done by SOPCBuilder.

To check the correctness of the initialization value of the startup barrier, a designer can do the following procedure:

• The designer creates the multicore system, including the Altera Avalon Mutex.

<sup>&</sup>lt;sup>7</sup>By default, the binary distributions of Erika Enterprise do not allow the possibility to remove the startup barrier.

- Then, the user have to check the value of the CPUID register for the first CPU. To do that, please open the PTF file containing the system description. Inside the MODULE section of the various CPUs, search for the WIZARD\_SCRIPT\_ARGUMENTS section. Look at the value for the attribute cpuid\_value: that is the CPUID value for the considered CPU.

- The value found in the previous step for the Master CPU must be equal to the *Initial Owner* that is set in the Altera Avalon Mutex dialog box (see Figure 3.3).

Warning: Typical behavior that shows up when the mutex initialization is not done in the proper ways is that the either system (all the CPUs) simply blocks at the startup barrier, or simply the barrier is not considered at all. The latter case is subtle because some of the processors could start to use the shared data structures when the CPU responsible for their initialization has not initialized them yet. In this case the early arriving processor could have read uninitialized values, and the values written could be overwritten by the initialization values.

**Warning:** Please note that the initialization value of the Altera Avalon Mutex done with the startup barrier is only valid when the system boots up the first time. When debugging a multicore systems with a startup barrier, the user have to reboot *all* the CPUs when starting a multicore debug system. Simply stopping the debugger and starting another debug session in the Nios II IDE is not sufficient, because the Altera Mutex is not reset.

### 3.7 Interprocessor Interrupt

Multicore Nios II systems using Erika Enterprise must include an Interprocessor Interrupt Controller in order for a CPU to notify events to other CPUs. For that reason, Evidence SRL supports interprocessor interrupt controllers for up to 32 processors, made using the standard Altera Avalon PIO SOPCBuilder Component.

Once included into the design, the Interprocessor interrupt feature will be used internally by Erika Enterprise. The developer does not have to care anymore about it.

The interprocessor interrupt is made by two main parts, the *input* part and the *output* part. It has to be created following these guidelines:

• First of all, the designer have to instantiate the *input* part of the Interprocessor Interrupt controller, that is basically an Altera Avalon PIO component for each CPU in the system. The component must be an input PIO, capable to raise an

interrupts on the rising edge of the input pin. Figures 3.4, 3.5, and 3.6 shows the settings to be used for each component. The components have to be connected to each CPU data master. The Interrupt priority should be the lowest among the priorities of the interrupts connected to a given CPU.

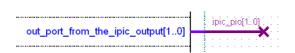

- Then, the designer have to instantiate the *output* part of the Interprocessor interrupt controller, that is basically a system wide Altera Avalon output PIO component. The component must have 1 output bit *for each* CPU in the system. Figure 3.7 shows a 2 CPU setting for this component. The component have to be connected to the data master of *all* the CPUs.

- After that, the input part and the output part of the Interprocessor Interrupt have to be connected together. The simplest way to do that is from the BDF file containing the SOPCBuilder Component. After generating the SOPCBuilder Component, please connect each output pin of the output PIO to a correspondent 1-pin input PIO. Figure 3.8 and 3.9 show a simple way to connect them using Altera Quartus II named pins. The pins have to be connected *in the same order specified in the CPUID register* of each CPU. That is, the CPU with CPUID 0 have to be connected to the pin 0 of the output PIO, and so on.

- Next, in the OIL configuration file, the CPU have to be listed (again) in the order of the CPUID register, that is the same order they are connected to the interprocessor Interrupt output pins, starting from 0. An example for the 2 CPU snapshots showed in Figure 3.8 and 3.9 is included below. The IPIC\_GLOBAL\_NAME contains the uppercase name of the IPIC output part, as listed in the system.h file generated by the Altera System Libraries. The IPIC\_LOCAL\_NAME contains the uppercase name of the IPIC input part, as listed in the system.h file generated by the Altera System Libraries.

```

CPU test_application {

OS EE {

MASTER_CPU = "cpu0";

IPIC_GLOBAL_NAME = "IPIC_OUTPUT";

CPU_DATA = NIOSII {

ID = "cpu0";

IPIC_LOCAL_NAME = "IPIC_INPUT_CPUO";

. . .

};

CPU_DATA = NIOSII {

ID = "cpu1";

IPIC_LOCAL_NAME = "IPIC_INPUT_CPU1";

. . .

};

. . .

};

```

| 👑 PIO (Parallel I/O) - ipic_input_0                                                               |

|---------------------------------------------------------------------------------------------------|

| PIO (Parallel I/O)                                                                                |

| Parameter<br>Settings                                                                             |

| Basic Settings > Input Options > Simulation >                                                     |

| Width                                                                                             |

| Width (1-32 bits): 1                                                                              |

| Direction                                                                                         |

| Input ports only                                                                                  |

| O Both input and output ports                                                                     |

| Output ports only                                                                                 |

| Output Port Reset Value                                                                           |

| Reset Value: 0x0                                                                                  |